# AN2622 Application note

## TS4909 low power stereo headphone amplifier evaluation board user guidelines

#### Introduction

This application note concerns the DEMOTS4909 evaluation board, designed to evaluate the TS4909 low power stereo headphone amplifier with capacitor-less output.

In this document, you will find:

- a brief description of the TS4909 audio amplifier

- a description of the evaluation board and all of its components

- the layout of the evaluation board

#### About the TS4909

The TS4909 is a stereo audio amplifier designed to drive headphones in portable applications.

The integrated phantom ground is a circuit topology that eliminates the heavy output coupling capacitors. This is of primary importance in portable applications where space constraints are very high. A single-ended configuration is also available, offering even lower power consumption because the phantom ground can be switched off.

Specially designed for applications requiring low power supplies, the TS4909 is capable of delivering 52mW of continuous average power into a  $32\Omega$  load with less than 1% THD+N from a 3V power supply. Pop & click noise during switch-on and switch-off phases is eliminated thanks to integrated circuitry.

Key features of the TS4909 include:

- No output coupling capacitors necessary

- Pop & click noise reduction circuitry

- Operating from V<sub>CC</sub> = 2.2V to 5.5V

- Standby mode active low

- Output power:

- 158mW @5V, into  $16\Omega$  with 1% THD+N max (1kHz)

- 52mW @3.0V into 32 $\Omega$  with 1% THD+N max (1kHz)

- Ultra low current consumption: 2.0mA typ.@3V

- Ultra low standby consumption: 10nA typ.

- High signal-to-noise ratio 105dB typ. @5V

- High crosstalk immunity: 110dB (F=1kHz)

- PSRR: 72dB (F=1kHz), inputs grounded

- Low t<sub>WLI</sub>: 50ms in PHG mode, 100ms in SE mode

- Available in lead-free DFN10 3x3mm

For complete information about the TS4909, refer to the datasheet.

September 2007 Rev 1 1/5

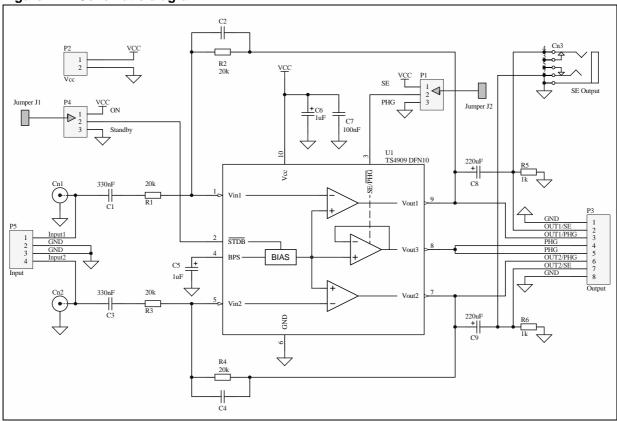

### 1 Description of the evaluation board

The DEMOTS4909 evaluation board is designed for the TS4909 low power stereo headphone amplifier with capacitor-less output.

The gain  $(A_V)$  is set at 1 V/V for both channels and can be adapted if necessary with a modification of R1 or R2 values for the Left channel, and R3 or R4 values for the Right channel.

Table 1. Gain per channel

| Channel | Gain (V/V)               |

|---------|--------------------------|

| Left    | $A_V = -\frac{R2}{R1}$   |

| Right   | $A_{V} = -\frac{R4}{R3}$ |

C1 with R1 (and C3 with R3) create an input high-pass filter with a cut-off frequency of 24.1Hz. C8 with a  $16\Omega$  load (and C9 with a  $32\Omega$  load) create an output high-pass filter with a cut-off frequency of 45.2Hz (22.6Hz). For information on how to change the value of the cut-off frequency, refer to the datasheet.

The C2 and C4 component locations are empty in order to add a low-pass filter if required.

Table 2. Evaluation board connectors

| Connector | Description                                                                                                                                                                                                                                                                         |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P1        | Connector for setting PHG or SE configuration of the TS4909:  - The pins 1 and 2 are shorted, output stage is in SE mode  - The connector pins are connected:  - 1 to V <sub>CC</sub> - 2 to SE/PHG control  - 3 to GND                                                             |  |  |

| P2        | Power connector (V <sub>CC</sub> and GND). Power supply voltage from 2.2V to 5.5V.                                                                                                                                                                                                  |  |  |

| Р3        | Output signal connector. The connector pins are:  - 1&2: SE output 1 (GND and active signal)  - 3&4: PHG output 1 (PHG reference voltage output and active signal)  - 5&6: PHG output 2(active signal and PHG reference voltage output)  - 7&8: SE output 2 (active signal and GND) |  |  |

| P4        | Standby control connector:  -   -   -   -   -   -   -   -   -   -                                                                                                                                                                                                                   |  |  |

| P5        | Input signal connector (GND and active input signal). Pins 1 and 2 for input 1 and pins 3 and 4 for input 2.                                                                                                                                                                        |  |  |

**Caution:** When you apply the power supply through P2, **do not** invert the polarity because it would destroy the amplifier at U1.

Figure 1. Schematic diagram

Table 3. Component list for the evaluation board

| Designation | Quantity | Description                              |

|-------------|----------|------------------------------------------|

| C1, C3      | 2        | 330nF/16V, ceramic capacitors, 0805      |

| C2, C4      | 0        | Not connected, 0603                      |

| C7          | 1        | 100nF/16V, ceramic capacitors, 0805      |

| C5, C6      | 2        | 1μF/50V, electrolytic capacitor          |

| C8, C9      | 2        | 220μF/10V, electrolytic capacitor        |

| P2          | 1        | 2-pin header 2.54mm pitch                |

| P3, P4      | 2        | 3-pin header 2.54mm pitch                |

| P3          | 1        | 8-pin header 2.54mm pitch                |

| P5          | 1        | 4-pin header 2.54mm pitch                |

| J1, J2      | 2        | Jumper, 2.54mm pitch                     |

| Cn1, Cn2    | 2        | Not connected, phono plug                |

| Cn3         | 1        | Not connected, stereo headphone jack 3.5 |

| U1          | 1        | TS4909                                   |

**47/**

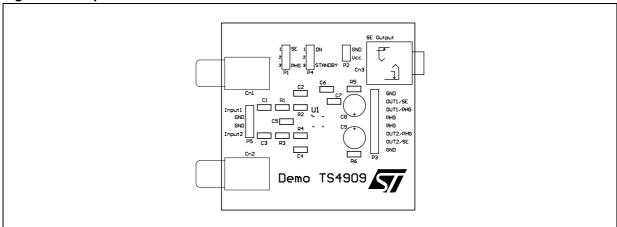

## 2 Evaluation board layout

The following schematics show the layers and the top view of the evaluation board.

Figure 3.

**PCB** bottom layer

Figure 2. PCB top layer

Demo TS4909

Figure 4. Top view of evaluation board

## 3 Revision history

Table 4. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 23-Sep-2007 | 1        | Initial release. |

**577**

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com